전체뉴스 1-10 / 2,263건

- 최신순

- 정확도순

- 과거순

-

케이던스 디자인 시스템즈 이사(director) 6억3880만원어치 지분 매도

... 및 경로, 최적화 및 다중 패터닝 준비와 같은 물리적 구현 도구; 실리콘 제조를 위한 준비가 된 것으로 디자인을 승인하기 위해 제품을 승인합니다. 또한 아날로그, 혼합 신호, 맞춤형 디지털, 메모리 및 무선 주파수 설계를 위한 트랜지스터 수준까지 회로의 도식 및 물리적 표현을 생성하기 위한 맞춤형 IC 설계 및 시뮬레이션 제품을 제공합니다. 인쇄 회로 기판 및 IC 패키지를 개발하고 전자기, 전열 및 기타 다중 물리학 효과를 분석하기 위한 시스템 설계 및 분석 제품. ...

한국경제 | 2024.04.18 06:28 | 굿모닝 로보뉴스

-

"상따했다가 물렸어요"…하루 만에 17% 폭락 '피눈물'

... 기판에 쓰인 플라스틱 등 유기 소재 대신 유리를 사용한 기판이다. 유기기판보다 데이터 처리량이 약 8배 많지만, 전력 소비는 절반가량 낮아 '꿈의 기판'으로 불린다. 인공지능(AI)이 급격히 확산하며 더 많은 트랜지스터를 집적할 수 있는 유리기판이 차세대 기판으로 관심을 끌었다. 이규하 NH투자증권 연구원은 "제이앤티씨는 글로벌 유리기판 소재 업체로 발돋움할 것"이라며 "제이앤티씨는 이미 글로벌 업체들과 공급을 논의하고 ...

한국경제 | 2024.04.11 07:35 | 진영기

-

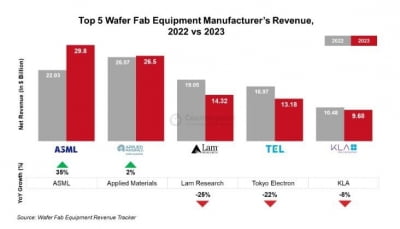

반도체장비 제조업체 상위 5곳 작년 총매출 감소…ASML 1위

... KLA(-8%)의 매출은 전년 대비 감소했다. 특히 ASML은 심자외선(DUV)과 극자외선(EUV) 장비 매출 호조에 힘입어 글로벌 1위를 기록했다. 지난해 파운드리 부문 매출은 게이트올어라운드(GAA·Gate All Around) 트랜지스터 아키텍처의 증가와 사물인터넷(IoT), 인공지능(AI), 클라우드, 자동차, 5G 등 여러 부문에 걸친 '성숙 공정'(Mature Node) 기기에 대한 투자 강화로 전년 대비 16% 증가했다. 메모리 부문의 매출은 전반적인 ...

한국경제 | 2024.04.09 11:58 | YONHAP

-

美, TSMC에 16조원 파격 지원…첨단반도체 공급망 자국유치(종합2보)

... 첫 번째 팹을 착공했고, 지난해에는 두 번째 팹 건설을 시작했다. TSMC는 이날 보도자료에서 "첫 번째 팹은 2025년 상반기에 4나노 기술을 활용한 생산을 시작할 예정이고, 앞서 발표한 3나노 기술에 더해 차세대 나노시트 트랜지스터를 활용해 세계 최첨단 2나노 공정 기술로 생산하는 두 번째 팹은 2028년 조업을 시작할 것"이라고 말했다. 이어 "세 번째 팹은 2나노 혹은 더 진보된 공정으로 2020년대 말부터 칩 생산을 시작할 것"이라며 세 곳의 팹이 첨단·고임금 ...

한국경제 | 2024.04.08 20:23 | YONHAP

-

반도체 파격 지원…美, TSMC에 16조원 제공

... 첫 번째 팹을 착공했고, 지난해에는 두 번째 팹 건설을 시작했다. TSMC는 이날 보도자료에서 "첫 번째 팹은 2025년 상반기에 4나노 기술을 활용한 생산을 시작할 예정이고, 앞서 발표한 3나노 기술에 더해 차세대 나노시트 트랜지스터를 활용해 세계 최첨단 2나노 공정 기술로 생산하는 두 번째 팹은 2028년 조업을 시작할 것"이라며 "세 번째 팹은 2나노 혹은 더 진보된 공정으로 2020년대 말부터 칩 생산을 시작할 것"이라고 밝혔다. 이와 관련, 지나 러몬도 ...

한국경제TV | 2024.04.08 20:15

-

美, 대만 TSMC에 반도체 보조금 9조원 등 16조원 지원(종합)

... 첫 번째 팹을 착공했고, 지난해에는 두 번째 팹 건설을 시작했다. TSMC는 이날 보도자료에서 "첫 번째 팹은 2025년 상반기에 4나노 기술을 활용한 생산을 시작할 예정이고, 앞서 발표한 3나노 기술에 더해 차세대 나노시트 트랜지스터를 활용해 세계 최첨단 2나노 공정 기술로 생산하는 두 번째 팹은 2028년 조업을 시작할 것"이라고 말했다. 이어 "세 번째 팹은 2나노 혹은 더 진보된 공정으로 2020년대 말부터 칩 생산을 시작할 것"이라며 세 곳의 팹이 첨단·고임금 ...

한국경제 | 2024.04.08 19:35 | YONHAP

-

케이던스 디자인 시스템즈 수석 부사장 겸 CFO(officer: Sr. VP & CFO) 91억3346만원어치 지분 매도

... 및 경로, 최적화 및 다중 패터닝 준비와 같은 물리적 구현 도구; 실리콘 제조를 위한 준비가 된 것으로 디자인을 승인하기 위해 제품을 승인합니다. 또한 아날로그, 혼합 신호, 맞춤형 디지털, 메모리 및 무선 주파수 설계를 위한 트랜지스터 수준까지 회로의 도식 및 물리적 표현을 생성하기 위한 맞춤형 IC 설계 및 시뮬레이션 제품을 제공합니다. 인쇄 회로 기판 및 IC 패키지를 개발하고 전자기, 전열 및 기타 다중 물리학 효과를 분석하기 위한 시스템 설계 및 분석 제품. ...

한국경제 | 2024.04.03 06:38 | 굿모닝 로보뉴스

-

'HBM 실수' 되풀이 안한다…삼성, 3D D램으로 135조 시장 반격

... 미세공정 기술이다. 네덜란드 ASML이 만든 극자외선(EUV) 노광장비를 활용해 칩에 회로를 보다 세밀하게 그리는 식으로 단위 면적당 용량을 끌어올렸다. 이 덕분에 최신 규격 D램인 DDR5에는 전작보다 3배 많은 620억 개의 트랜지스터(셀 안에서 전자 흐름을 제어하는 장치)가 수평으로 들어간다. 그러자 또 다른 숙제가 생겼다. 빽빽하게 셀을 욱여넣다 보니 전류 누설, 트랜지스터 간 간섭 같은 부작용이 생긴 것. 삼성전자가 지난달 26~28일 열린 글로벌 반도체 학회 ...

한국경제 | 2024.04.02 18:26 | 황정수/김채연/박의명

-

삼성 '3D D램' 내년 공개…"다시 초격차"

... 개발 로드맵을 발표했다. 3D D램은 D램 내부에 있는 셀을 수직으로 쌓은 한 개의 D램이라는 점에서 D램 완제품을 여러 개 쌓아 용량을 늘린 HBM과는 다른 개념이다. 로드맵에 따르면 삼성은 2025년 ‘수직 채널 트랜지스터(VCT)’ 기술을 활용한 초기 버전의 3D D램을 선보일 계획이다. VCT는 셀을 구성하는 트랜지스터에서 전자가 흐르는 통로인 채널을 수직으로 세우고 이를 스위치 역할을 하는 게이트로 감싸는 기술이다. 커패시터를 포함한 ...

한국경제 | 2024.04.02 18:24 | 황정수/김채연/박의명

-

"中, ASLM 극자외선 장비없이 5나노 반도체 생산 기술 진전"

... 없이 첨단 반도체를 생산하기 위한 노력이다. 중국 반도체 공급망에 속한 다수 기업이 참여한 이런 시도는 최근 예비 연구에서 진전을 나타냈다. 여기에는 화웨이가 지난달 공개한 '자가 정렬 4중 패턴화'(SAQP) 특허가 사용됐다. 트랜지스터 밀도와 반도체 성능을 높이기 위해 라인을 여러 개 그리는 기술이다. 중국국가지식재산권국에 제출된 특허 신청서에는 첨단 식각과 리소그래피를 결합한 이 기술이 회로 패턴의 디자인 자유도를 높인다고 설명돼 있다. SAQP 기술을 사용하면 ...

한국경제 | 2024.04.02 10:27 | YONHAP